A Monte Carlo simulation approach to multiple services demand forecasting can be shown to reproduce the mean demand for services as calculated from the logit or probit model.

Numerical device simulation is based on the solution of a coupled system of nonlinear partial differential equations (PDEs) that can be either transient or static, or even involve complex quantitie

Desktop conferencing is a term used to describe real-time, computer-based conferences in which users may share data through their personal computers.

High dose, low energy (4x10 sup 15 cm sup -2 at 15 KeV ) arsenic ion implantation into silicon was performed in batch and single wafer mode using medium and high current ion implanters.

CdTe has been grown on (100) GaAs by molecular beam epitaxy (MBE), organometallic vapor phase epitaxy (OMVPE), and photo- assisted OMVPE (POMVPE).

Connecting each house to a broadband access network represents an unprecedented opportunity to offer added-value services and broadband Internet access to residential users and expand the customer

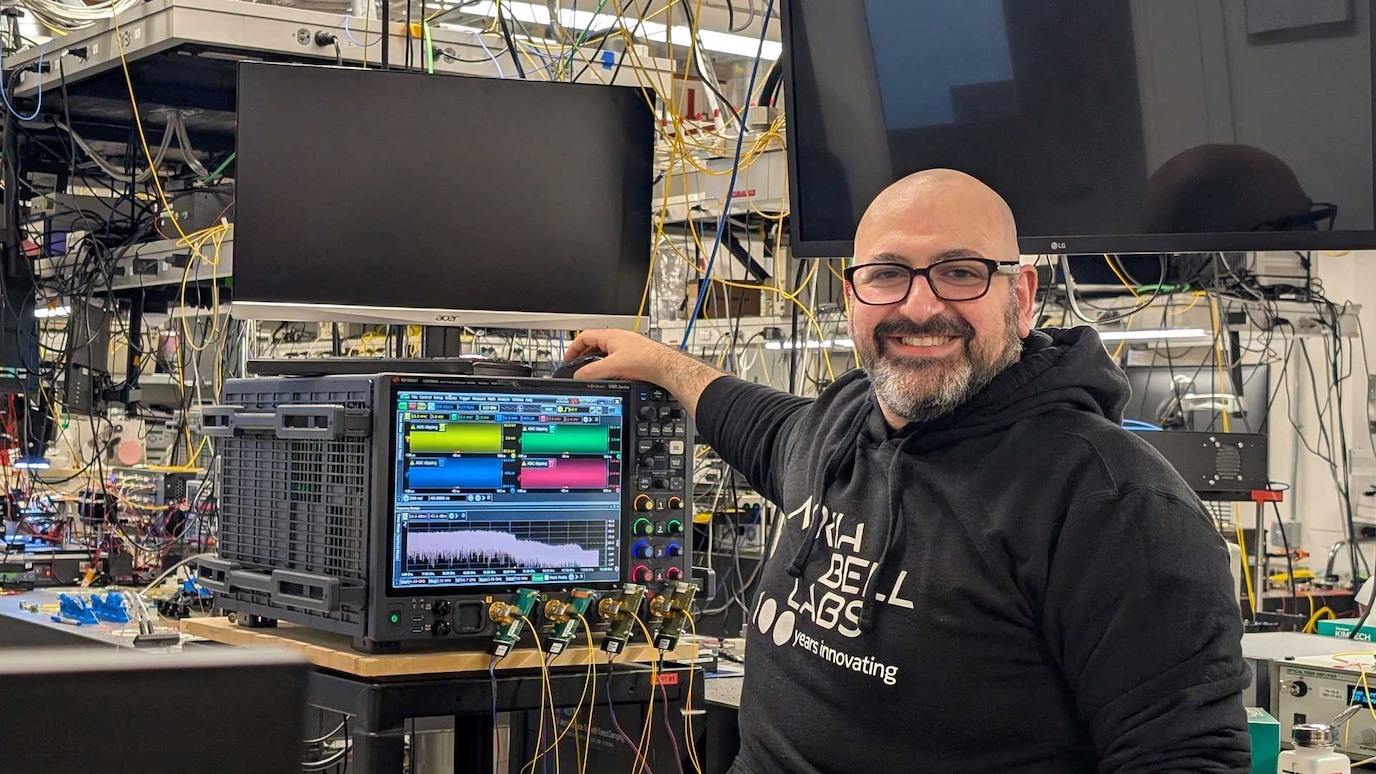

This paper investigates different power-saving mechanisms in ONUs and OLTs for point-to-point (PtP) optical access networks and time-division multiplexed passive optical networks (TDM-PONs).

This paper reports the early stage of de hot carrier degradation behaviour of n-channel low doped drain metal oxide semiconductor field effect transistors in a range of deep sub-micron technologies

Environmental contaminants can cause failures in telephone switching systems, computers, and other sophisticated electronic equipment.

We propose optimal resource allocation algorithms for two kinds of optical slot switching metro rings: fixed mixed line rate (fMLR), where the rate of each transponder (TRX) is fixed and set at net