Many manufactured products are 100 per cent tested with the idea of insuring that each unit of product meets the performance specifications.

We propose a method for differential transmission with multiple basestation antennas.

I N connection with many telephone problems of an economic character, it is necessary to develop methods for making estimates and forecasts of the effects of changes in conditions.

HE analysis of transmission circuits with which telephone engineers are familiar is an outgrowth of the general physical theory of the propagation of wave disturbances in continuous media.

in acoustics during past few years has caused acoustic impedance same relative THE progressimpedancemeasurementthetoin have the work has had importance that measurement electrical for many years.

I T H the increasing interest in wide-band amplifiers and circuits for microwave communication systems the measurement of the transfer phases of such components lias become a necessary procedure.

This paper deals with a method for QoE evaluation for the services transmitting large amount of data perceived by the end user in relatively short time periods, e.g.

This paper outlines a method of rating manufactured product.

A Method of Sampling Inspection By H. F. DODGE and H. G.

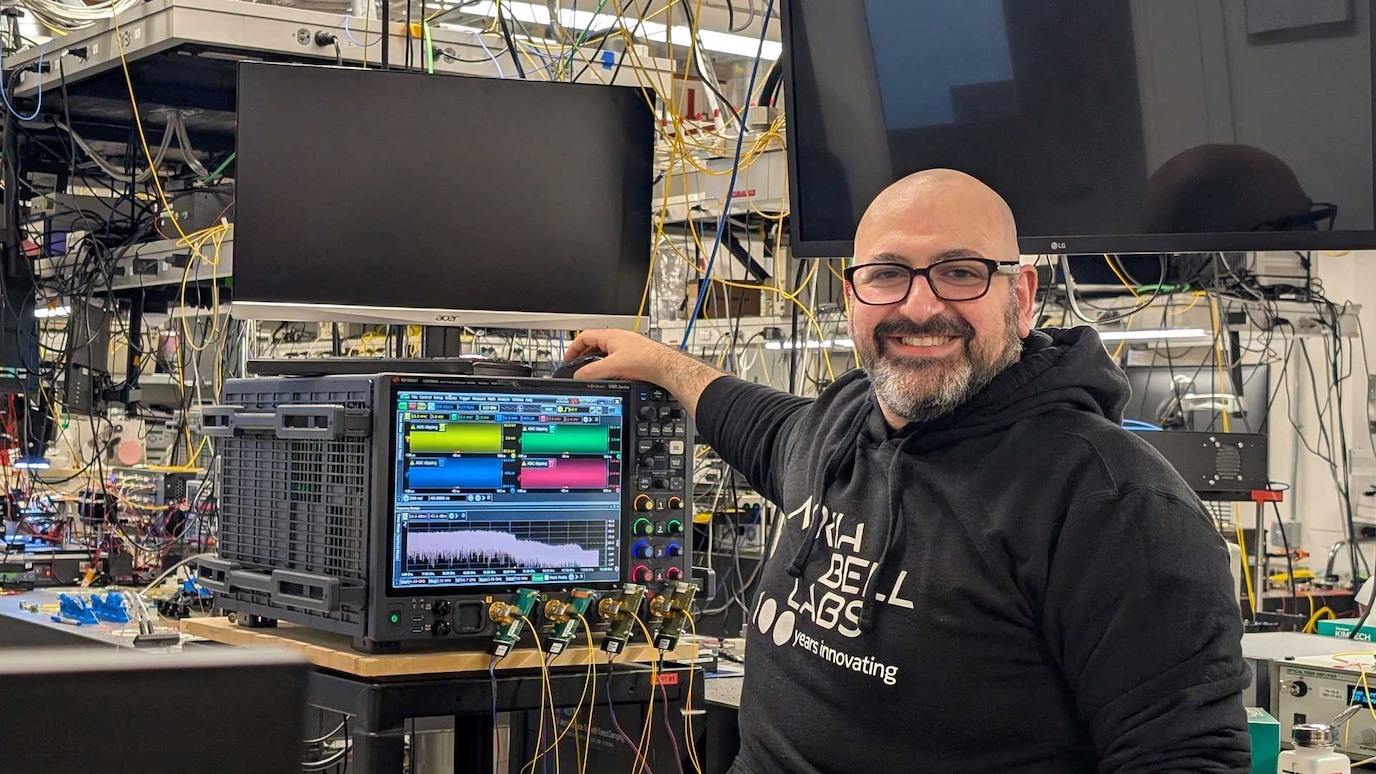

A Method to Characterize the Mechanical Properties of Undersea Cables By T. C.